Fast TSC calibration failed

El Time Stamp Counter (TSC) es un registro de 64 bits presente en todos los procesadores x86 desde el Pentium. Cuenta el número de ciclos desde cero.

Este contador de marca de tiempo ha sido hasta hace poco un recurso preciso y ligero para obtener información de tiempo de la CPU. Con la llegada de CPUs multi-core/hyper-threaded, sistemas con múltiples CPUs, y sistemas operativos con posibilidad de hibernación, el TSC no puede ser invocado para proporcionar resultados precisos y ha de tenerse mucho cuidado para corregir los posibles defectos: Si todos los núcleos (procesadores) tienen valores de tiempo idénticos en los registros. No hay garantía de que los contadores de marca de tiempo de múltiples CPUs en una misma placa base estén sincronizados. En estos casos, sólo se pueden obtener resultados fiables mediante el bloqueo de su código para una sola CPU. Incluso entonces, la velocidad de esa CPU puede cambiar debido a las medidas de ahorro energético adoptadas por el sistema operativo y/o por la BIOS, o si el sistema entra en hibernación y luego se reanuda. En estos últimos casos, para mantener su relevancia, el TSC debe ser recalibrado periódicamente.

Si durante el arranque del sistema ves un aviso de error igual o similar a este:

tsc: Fast TSC calibration failed

Puedes ignorarlo… Sólo está informando de que falló el primer intento de calibración. Puedes comprobar que posteriormente lo consiguió echándole un vistazo a /var/log/messages:

~# cat /var/log/messages | grep TSC

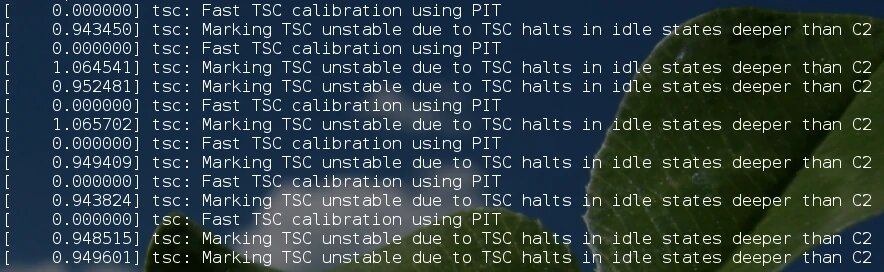

La salida debería mostrar resultados exitosos de la calibración del TSC… O no. Por ejemplo:

tsc: Fast TSC calibration using PIT

tsc: Marking TSC unstable due to TSC halts in idle states deeper than C2

Si hago un

~# cat /sys/devices/system/clocksource/clocksource0/available_clocksource

Devolverá

hpet acpi_pm

Si hago un

~# cat /sys/devices/system/clocksource/clocksource0/current_clocksource

Devolverá

hpet

Si es así, todo está bien, no te compliques demasiado la vida. Puedes ignorar este error.

Si no estás conforme, te recomiendo la lectura del siguiente artículo, en inglés, de Ravi Murty (Intel) : Eliminate the dreaded “clocksource is unstable” message: Switch to TSC for a stable clock source option for Linux when using an Intel® Xeon Phi™ Coprocessor .